TOWA Compression Molding Unit Added

Integra Technologies is excited to announce the addition of a TOWA Compression Molding unit to their Silicon Valley facility. The unit

Laser Grooving Service

Integra Technologies is excited to announce the addition of Laser Grooving to their long line of product offerings

Supplier Excellence Award

Integra is proud to have been recognized by Northrop Grumman for our successful supplier partnership. Recognized for Quality Excellence,

Integra Selected to Participate with NCMS for Second Year

Integra Selected to Participate with NCMS on Developmental Program for Silicon Photonics

Brett Robinson, Wichita Business Journal Executive of the Year 2023

The Wichita Business Journal recognized Brett Robinson, CEO and President of Integra Technologies, Inc., as one of its 2023 Executives of

Integra Technologies Adds FC150 Automated Die / Flip Chip Bonder

With Heterogeneous Integration and finer flip chip pitches becoming a reality, Integra Technologies recently added a FC150 Automated

Integra Technologies on CNBC

Thank you CNBC for highlighting Integra on the one year anniversary of the CHIPS Act this month. We are thankful for the efforts of all our

Integra Technologies Adds Vice President of Quality

Integra Technologies is excited to have Don Warring join the Integra team as the Vice President of Quality. Don is an industry veteran

Integra Technologies Announces Site in Wichita Region

Integra Technologies Announces Site in Wichita Region for Largest U.S. OSAT Semiconductor Project Bel Aire, Wichita and Sedgwick

BREAKING: Integra Selects Kansas for Largest OSAT Semiconductor Project

Integra Technologies Selects Kansas for Largest OSAT Semiconductor Project Kansas State Finance Council’s APEX vote paves way for

ISO/IEC 17025:2017 Certificate of Accreditation

Integra Technologies recently received the ISO/IEC 17025:2017 Certificate of Accreditation from the ANSI National Accreditation Board for

Comprehensive Testing of Connectors

Integra Technologies offers a full range of Qualification, Design Verification, and Reliability Testing for the harsh environments required

Integra Expands Growing Line of Burn-in and Life Test Equipment

Integra Technologies is pleased to announce the addition of a Tahoe Burn-in System to meet the growing technical demand of burn-in and life

Integra and the Artemis Orion Spacecraft

Integra Technologies and the Artemis Orion Spacecraft

Integra's Albuquerque facility moving into Integra's Wichita facility

Dear Integra Technologies' DPA, Failure Analysis and Qualification Customers using Integra Albuquerque, NM facility -

Integra Completes Purchase of Presto Engineering's US Based Test Assets

Silicon Valley, CA, March 31, 2022: Integra Technologies is pleased to announce the completion of the purchase of Presto Engineering’s

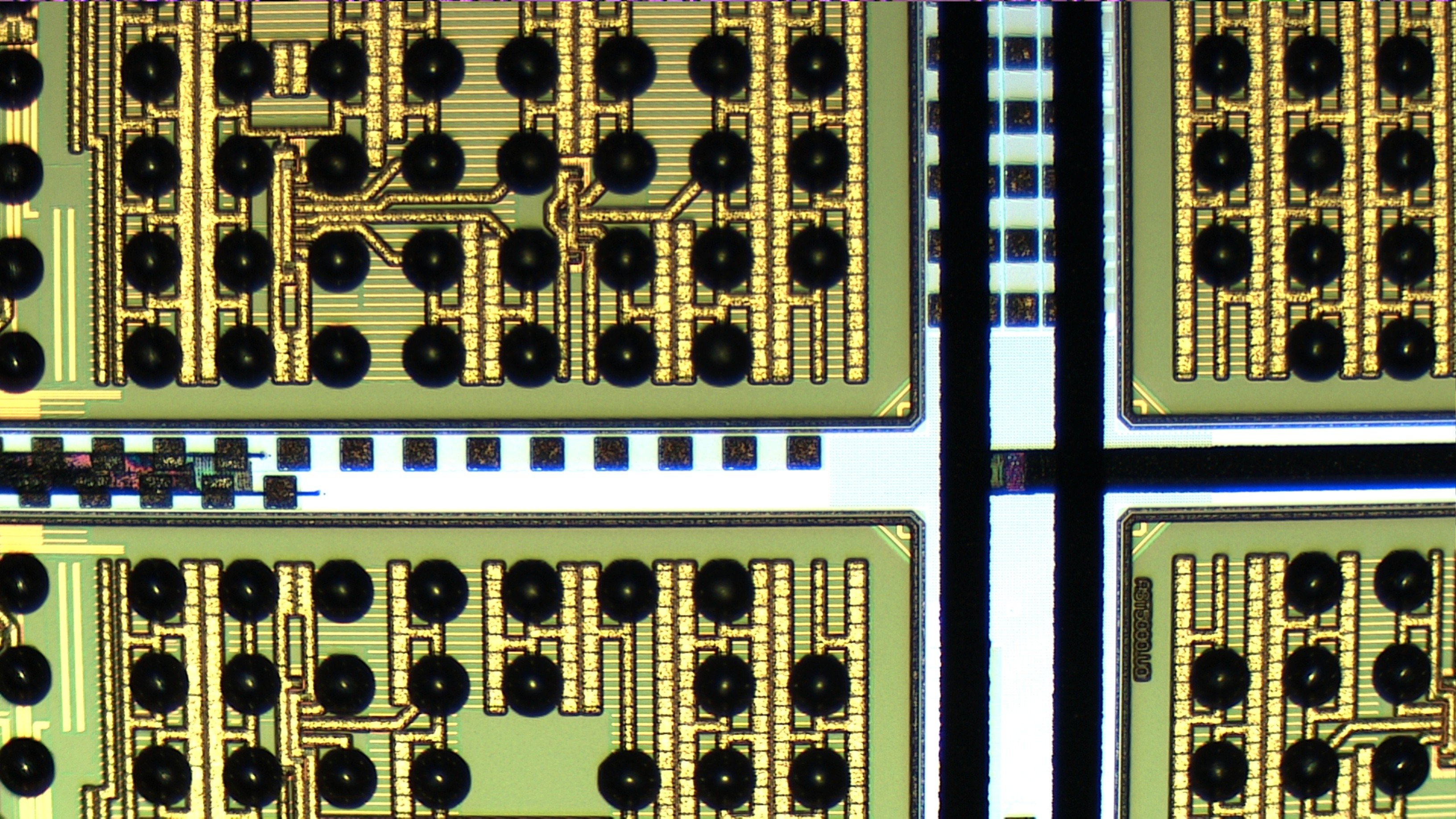

INTEGRA TECHNOLOGIES SILICON VALLEY ADDS NEW FLIP CHIP BONDER

Silicon Valley, CA (Aug 18, 2021) - Integra Technologies, a world leader in semiconductor packaging, assembly, test, characterization,

PRESS: Integra Technologies Adds V93000 SmartScale Tester

INTEGRA TECHNOLOGIES ADDS V93000 SMARTSCALE TESTER The addition of this SmartScale Test system allows Integra to now support their

INTEGRA TECHNOLOGIES EXPANDS SILICON PHOTONICS CAPABILITIES

INTEGRA TECHNOLOGIES EXPANDS SILICON PHOTONICS CAPABILITIES Silicon Valley, CA (Feb 9, 2021) - Integra Technologies, a world leader in

Webinar: Die Prep Processes and Overview

WEBINAR: DIE PREP PROCESSES AND OVERVIEW WEDNESDAY, DECEMBER 2, 2020, 1:00 P.M. PST

Upcoming Webinars From Integra Technologies

Sign up now for one of Integra's Webinars coming up this month: By request, Integra Technologies will be offering the

Webinar: Mil-Std-1580 DPA

Due to popular demand we will be presenting the webinar: Mil-Std-1580 DPA Including Copper Bond Wire PEMs AGAIN! Wednesday, Sep

INTEGRA TECHNOLOGIES NAMED TO THE 2020 INC. 5000 LIST

Inc. Magazine Unveils Its Annual List of America’s Fastest-Growing Private Companies—the Inc. 5000 Integra Technologies Ranks on the 2020

Integra Technologies Secures $20.7 Million F-35 Contract

INTEGRA TECHNOLOGIES SECURES A $20.7 MILLION CONTRACT AWARD FROM F-35 JOINT STRIKE FIGHTER PROGRAM OFFICE

INTEGRA TECHNOLOGIES SECURES A $20.7 MILLION CONTRACT AWARD FROM F-35 JOINT STRIKE FIGHTER PROGRAM OFFICE

*All contract work to be done at Integra's 250 employee Wichita facility*

WEBINAR: Obsolescence Management for EEE Parts

Join Integra, Wednesday, July 29th, at 1:00 p.m. PST to learn more about the Obsolescence Managemnet for EEE Parts

INTEGRA TECHNOLOGIES WINS $3 MILLION CONTRACT AWARD FROM NORTHROP GRUMMAN

*U.S. Senator Jerry Moran congratulates Integra, looks forward to seeing additional military related manufacturing in Wichita*

Integra Wins $3 Million Contract Award From Northrop Grumman

U.S. Senator Jerry Moran congratulates Integra, looks forward to seeing additional military related manufacturing in Wichita Wichita, KANS.

Obsolete Parts Management with Integra Technologies

Integra’s Parts Management Program (PMP) started in 1991, actively managing multiple Aerospace and Defense companies’ parts procurement

WEBINAR: Standards of PEM Qual and Technical Requirements Review

Standards of PEM Qual and Technical Requirements Review Integra is the leader in performing PEM (Plastic Encapsulated Microcircuits)

Expanded RF Services from Integra

Whatever your specific RF requirements, Integra can help. For over 35 years, Integra has been an integral part of our customers

Construction Analysis from Integra Technologies

Construction Analysis from Integra Technologies Construction Analysis gives a detailed view of the construction quality and materials used

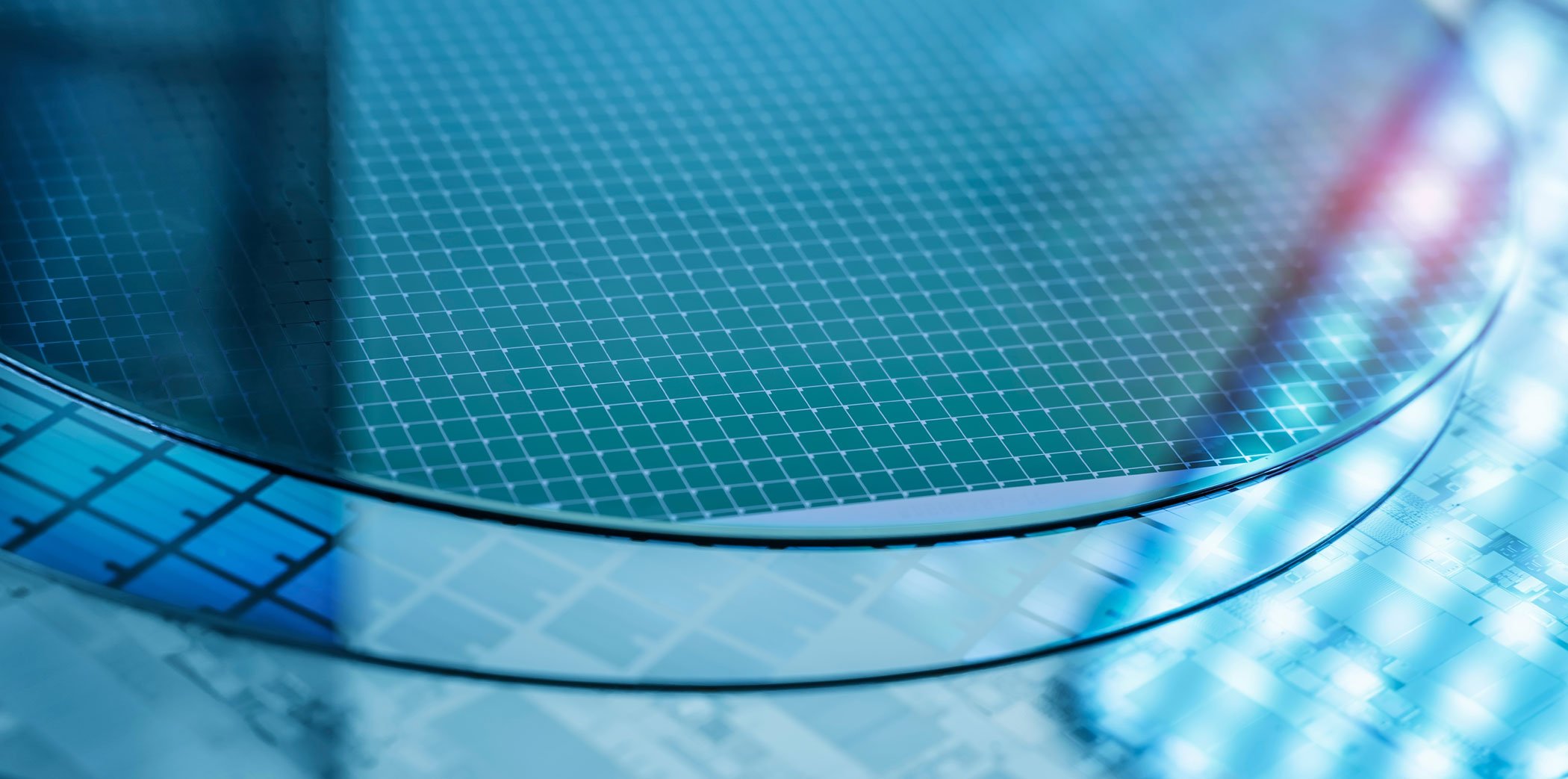

Die Prep Services from Integra

DIE PREP SERVICES Integra Technologies Silicon Valley, previously CORWIL Technologies, specializes in ultra-thin precision wafer thinning

Case Study: Saluda Medical

CASE STUDY: Integra has been an indispensable part of Saluda Medical’s growth and ongoing successes towards commercialization of the

ISTFA - Portland, Going on Now!

Stop by Booth #203 at ISTFA at the Portland Convention Center today and tomorrow to say 'Hi' to Sultan and Mark! Let them help you with

Integra is at IMAPS Boston NOW!

Stop by booth #401 at IMAPS Boston today and tomorrow and say Hi to John and Richard. They are eager to discuss Integra Technologies'

Integra Technologies at IMAPS Today!

Visit Integra Technologies September 30 - October 3 - Boston, MA - Booth #401 As a high-performance IC packaging provider, Integra

IMAPS Advanced System and Technology Conference Follow Up

Thank you to all who visited us last week at the IMAPS Advanced System and Technology Conference. It was a great turn out and we enjoyed

Visit Us at the IMAPS Advanced System in Package Technology Conference and Exhibition June 25-27

Integra's System-in-Package & MCM solutions offer the capabilities of a complete system in one device. As a high-performance

Heterogeneous Integration Roadmap Symposium 2/21-2/22

There was a great turn out at this year's Heterogeneous Integration Roadmap Symposium in Milpitas, CA last week. We would like to thank all

MEPTEC Symposium Today!

Stop by the Integra booth today and say hello to Rafi, Chip and Richard, 9:30 - 6:30 p.m.

MEPTEC Symposium, December 5

Visit Integra Technologies at MEPTEC's 'Heterogeneous Integration' Symposium, this Wednesday, December 5th from 8:00 - 5:00 with exhibits

ISTFA Going on Now!

ISTFA is going on now at the Phoenix Convention Center. Stop by booth #731 and say Hello!

-55°C Electrical Testing from Integra

Integra Technologies uses its advanced automated test equipment (ATE) for the purpose of testing at -55°C and beyond. In support of

INTEGRA TECHNOLOGIES ANNOUNCES NEW WEBSITE LAUNCH

The new and completely redesigned website offers visitors richer insight into Integra’s compelling capabilities in die preparation,

Open House TODAY!

Stop by and say 'hello' to the Integra group - facility tour, food and drinks! 3:00-7:00 p.m.!

OPEN HOUSE - June 19th!

Join us for an Open House at our Milpitas, CA facility Tuesday, June 19th! The Open House includes facility tours, wine tasting and hors

Case Study: GaN Wafer Dicing

CHALLENGE:To develop a singulation process for GaN wafers that consistently provides high quality and yields.

GSA Silicon Summit

Visit Integra this Thursday at the GSA Silicon Summit! Stop by Booth 10 and tell Joe, Ron and Jeff hello!

Visit Integra Technologies at DMSMS 2017, Booth #920

Integra Technologiesprovides a complete portfolio of turn-key services to support Military/Space/Aerospace companies threatened with

New Signs are up!

The new signs are in place at Integra Technologies! Stop by and take a look. Thank you Cordero Printing.

Going Green

Integra Technologies Silicon Valley (formerly CORWIL Technology) has partnered with Mynt Systems to take part in helping the environment by

Over 1 Million CSPs Assembled

MILPITAS, CA, October 10, 2017 – Integra Technologies (formerly CORWIL Technology) announced today that it has successfully produced over 1

Case Study: Captive Line

Read about how CORWIL Technology provided an in-house turnkey solution for a top fabless networking company that needed to implement volume

See What CORWIL Has to Offer

In response to the requests we’ve received about our processes and types of equipment we have, CORWIL has created aYoutube Channelto show

CORWIL Adds FTI 1000 Tester - Good to 3600V and Testing of Power Devices

CORWIL Technology (CORWIL) has teamed with Focused Test, Inc. to release the FTI 1000. The FTI 1000 tester adds to a growing variety of

CORWIL's Commitment to it's Customers

When CORWIL was approached by a medical customer that had developed a product that required a very small and strong die, CORWIL

Device Test and Package Solutions for Silicon Photonics

CORWIL Technology’s pursuit of cutting edge technology and prime location in the heart of Silicon Valley has led them to secure programs

CORWIL Invests in Portable Clean Environment

To satisfy customer demand for ultra-clean environments for wafer sort, CORWIL Technology (CORWIL) has added a Portable Clean Environment

CORWIL Technology Receives Trusted Accreditation

Milpitas, CA, October 19, 2016 – CORWIL Technology (CORWIL), headquartered in Milpitas, CA, has received Trusted Accreditation by the

Medical Electronics Symposium 2016

Visit us at SMTA's Medical Electronics Symposium, September 14 & 15 at Marylhurt University in Portland, Oregon. This year's Key Note

Reliability Testing from CORWIL Technology

What's NEW... CORWIL can now perform ALL JESD22-A113 Precondition work IN-HOUSE, as well as before and after CSAM with the Sonoscan D9000.

Dice Before Grind (DBG) for Medical Devices

CORWIL was recently approached by a medical customer who had developed a tiny wearable device that included a small bare die with

CORWIL INCREASES WAFER SORT CAPABILITY

Milpitas, CA, April 27, 2016 – CORWIL Technology (CORWIL) continues to demonstrate its full turnkey capabilities for its customers by

CORWIL Technology Receives Recognition from Device Engineering Incorporated

CORWIL TECHNOLOGY RECEIVES A PERFECT SCORECARD FROM DEVICE ENGINEERING INCORPORATED Milpitas, CA, March 16, 2016 – CORWIL Technology

Processing III-V and Other Non-Silicon Materials

CORWIL Technology successfully processes a number of materials through its wafer processing facility. While Silicon is the majority of

CORWIL Technology Receives Excellent Performance Report Card from Microsemi Corporation

CORWIL Technology Receives Excellent Performance Report Card from Microsemi Corporation Milpitas, CA July 21, 2015 - CORWIL Technology

CORWIL Technology Producing Volume Plastic Parts Including MicroSD and QFN

Milpitas, CA June 18, 2015 - CORWIL Technology announced today that it has more than doubled its QFN production in 2015 and recently

CORWIL Technology Receives Quality Management System

Milpitas, CA, May 6, 2015 - CORWIL Technology announced today their Certification to the Aerospace Quality Management System, AS9100C,

CORWIL TECHNOLOGY TEST, RELIABILTY AND EOL SERVICES

Milpitas, CA, March 11, 2015 - CORWIL Technology has fully integrated Test, Reliability and EOL services along with wafer preparation and

Assembly and Test Open House Success

Thank you to all of our customers, colleagues and friends who attended our Open House on Wednesday! Visitors were able to take a tour of

CORWIL Technology Selected as Supplier of the Year by Inphi Corporation

Milpitas, CA, February 4, 2015– CORWIL Technology (CORWIL), the premier US based, IC assembly and test services subcontractor, offering

CORWIL Technology Combines Assembly and Test in One Location

Milpitas, CA, December 18, 2014 - CORWIL Technology now offers assembly and test services to their customers all under one roof. CORWIL

Die-Prep Considerations for IC Device Applications

Earlier this month, CORWIL's own Jonny Corrao, Engineering Manager, presented 'Die-Prep Considerations for IC Device Applications,' at the

INTEGRA TECHNOLOGIES SELECTED BY THE DEPARTMENT OF DEFENSE MISSILE DEFENSE AGENCY TO COMBAT COUNTERFEIT ELECTRONICS

WICHITA, KS - Oct 21, 2014 - Integra Technologies LLC, a world leader in integrated circuit test and related services, announced today that

CORWIL Focuses on MedTech Industries

CORWIL Technology is a U.S. based OSAT with a unique focus on Medical Device and Biotech industries. Our Bay Area facilities are state of

CORWIL Increases Die Attach Capacity with a New MAT 6400

Milpitas, CA, March 31, 2014 – CORWIL Technology (CORWIL) announces continued invest ment in capabilities with the addition of a new MAT

CORWIL Increases Molding Capabilities with a FICO MMS-W Molding System

CORWIL INCREASES MOLDING CAPABILITIES WITH A FICO MMS-W MOLDING SYSTEM Milpitas, CA, November 22, 2013 – CORWIL Technology announced the

Want to Learn More About Die Singulation?

Die singulation is the process of isolating individual IC’s from a wafer. There are a variety of methods for die singulation with the most

INTEGRA TECHNOLOGIES APPROVED BY DLA FOR MIL-STD-750 PROCESSING

WICHITA, KS - Oct 13, 2013 - Integra Technologies, a world leader in integrated circuit test and related services, is pleased to announce

What is Wafer Thinning?

Wafer thinning is the process of removing material from the backside of a wafer to a desired final target thickness. The two most common